ChipGPT is a new scalable framework that automates the hardware design process by using ChatGPT without any retraining or fine-tuning. It assists the hardware engineers to design logic circuits more efficiently using natural language specifications. We tell the computer what kind of chip we want and let the computer design the hardware logic for us.

ChipGPT generates Verilog programs (hardware descriptions) from natural language prompts (user inputs).

To improve the quality of prompts and outputs, ChipGPT introduces a prompt generator before ChatGPT and an output manager after, achieving these enhancements without direct manipulation of the large language model (LLM).

ChipGPT was evaluated on several natural language specifications and compared with existing methods and native LLMs. The results show that ChipGPT can generate hardware logic designs that match the natural language specifications better than the others. It also shows that ChipGPT can make the design process easier and more flexible, and can explore more design options to find the best one.

ChipGPT was evaluated on several natural language specifications and compared with existing methods and native LLMs. The results show that ChipGPT generates hardware logic designs that better align with natural language specifications than other approaches. Additionally, ChipGPT simplifies the design process, enhances flexibility, and explores a broader range of design options to identify the best solution.

The model

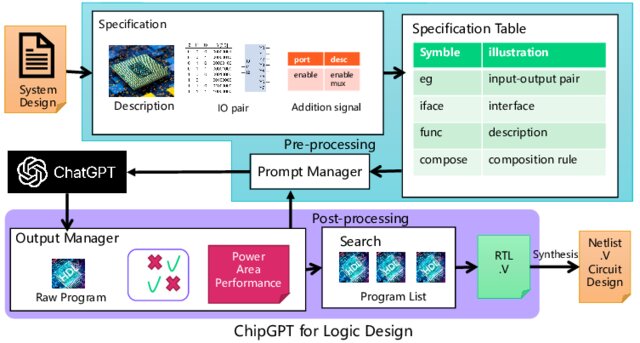

ChipGPT does not require retraining or fine-tuning. Its workflow consists of four stages: prompt generation, program generation, program optimization, and design selection (see the picture below).

- Prompt generation: it creates prompts for the ChatGPT based on specification description given by the user (ex: “Design a 4-bit adder with carry-in and carry-out”).

- Program generation: it uses ChatGPT to generate the Verilog code for each prompt.

- Program optimization: an output manager fixes and improves the Verilog code (raw program) through machine feedback and human feedback and puts them together in a final design space (program list). This space contains all the possible solutions.

- Design selection: ChipGPT searches through this final design space and picks the best design according to the target metrics.

Hardware design methods

The process of creating the logic circuits that make up a chip, such as a microprocessor or a memory device is complex and requires a high level of expertise and skill. There are two main approaches that aim to speed up and simplify this process (see table below):

- Programming language-based methods that use higher-level languages to describe the hardware logic and functionality. Some examples include Chisel, Spatial, SuSy, and ScaleHLS. These methods do not accept natural language expressions, which still require manual programming skills.

- Program synthesis based methods that use high-level descriptions to automatically generate computer programs. For example, Bosy is a tool that can generate Verilog code from formal specifications.

| Agile Logic Design Method | Representative Works |

|---|---|

| Programming language based hardware design | Chisel, Spatial, SuSy, ScaleHLS |

| Program Synthesis based hardware design | BoSy, Bounded Synthesis |

These languages are designed to describe the circuits at the register-transfer level or the behavior and structure of the chip in a detailed and precise way. However, they are often very complex, verbose, and hard to learn and use.

The use of LLMs for hardware design

To overcome these limitations, the researchers and developers have explored the idea of using large language models (LLMs) to generate hardware logic designs from natural language specifications.

By enabling designers to articulate their requirements in natural language, the chip design process could become more intuitive and user-friendly, potentially allowing for greater innovation and sophistication in chip designs.

Natural language is more accessible and flexible than low-level programming languages. The designers can express design requirements in simple sentences. It can also capture the intent and meaning of the designer more easily and directly.

For example, instead of writing a long and complicated code in Verilog to implement a simple CPU, one could simply write a natural language specification like: “A simple CPU that can perform arithmetic and logical operations on 8-bit operands”.

Power, Performance, and Area (PPA) metrics

PPA metrics are crucial factors that determine the quality and efficiency of a hardware design solution. Power is the amount of energy that a chip uses when it works. Performance is how fast and well a chip does its functions and tasks (speed, latency, and computation power). Area is the amount of space that a chip occupies on a silicon wafer.

In the next figure, the red area shows the ideal PPA results for a program, while programs created by LLMs like ChatGPT stay in their Initial State because they do not consider PPA metrics when they are trained.

To solve this problem, they developed the output manager. It improves the programs created by LLMs for PPA metrics and promotes them from the Initial State to the Optimize State (yellow area).

The post-addition principle

ChatGPT was trained for generating only raw programs. So the researchers added some extra rules to help ChatGPT improve its output.

One of these rules is the post-addition principle. This is a rule for generating prompts to produce valid and optimal Verilog code. It states that the handshake signals, which are signals that control the data transfer between modules, should be added to the prompt after the main logic design is generated by the language model.

In the left column of the figure above (no post-addition), the handshake signals are added to the same prompt. However, the generated implementation by the language model is incorrect, as it includes an output port called “valid” which is not allowed in this context.

How ChipGPT controls the output

ChipGPT does not try to change the raw program generated by GPT directly, because it may not be correct or easy to analyze and modify. Instead, it lets GPT generate different versions of the code (PPA0, PPA1, PPA2…) and refines them to get the final output. The workflow of this process is shown in the figure below.

In the figure we can see the four modules used by ChipGPT to control the output: Specification Split, Prompt Manager, Output Manager, and Enumerate Search.

Specification Split and Prompt Manager work before GPT is called to handle the natural language specifications and generate prompts for GPT.

Output Manager and Enumerate Search work after GPT is called to handle the design constraints and select the best version of the code based on power, performance, and area metrics.

ChipGPT repeats these steps for each iteration until it gets the final output that satisfies the specifications and the constraints.

Evaluation results

The authors wanted to see how well ChipGPT and LLMs can design hardware using natural language. They used GPT-3.5 and wrote their input programs in SystemVerilog. They also tested ChipGPT on different kinds of hardware design problems and compared it with other existing methods for hardware design.

In the area target optimization mode (PPA), ChipGPT achieves a significant 47% reduction in size compared to the original ChatGPT. The results indicate that ChipGPT offers improvements in terms of programmability, controllability, and design optimization space compared to previous approaches and standalone native LLMs.

Conclusion

ChipGPT is a new framework that uses LLMs (ChatGPT) to generate hardware logic designs from natural language specifications.

Natural language logic design is a new frontier for hardware development that can make hardware logic design more accessible, efficient, and creative.

Learn more:

Paper on arXiv: “ChipGPT: How far are we from natural language hardware design”